Izraz VLSI pomeni 'zelo velika integracijska tehnologija', ki vključuje oblikovanje integriranih vezij (IC) z združevanjem tisočih tranzistorji logično v en čip različna logična vezja . Ti IC-ji sčasoma zmanjšajo zaseden prostor vezja v primerjavi s tokokrogi z običajnimi IC-ji. Računska moč in izkoriščenost prostora sta glavna izziva zasnove VLSI. Izvajanje projektov VLSI odpira zahtevno in svetlo kariero tako za študente kot za raziskovalce. Nekatera nova trendna področja VLSI so Poljsko programljivo matriko vrat aplikacije (FPGA), zasnove ASIC in SOC. Spodaj je seznam nekaterih projektov VLSI za tiste študente, ki resnično iščejo projekte na tem področju. Ta članek obravnava pregled projektov VLSI, ki temeljijo na FPGA, Xilinx, IEEE, Mini, Matlab itd. Ti projekti so v veliko pomoč študentom tehnike, študentom M.tech-a.

Projekti VLSI za študente tehnike

V nadaljevanju so obravnavani projekti VLSI z izvlečki za študente elektronike.

VLSI projekti

1). Transformacija diskretnega valovanja na osnovi 3D dviganja

Ta projekt pomaga pri zagotavljanju zelo natančnih slik z uporabo kodiranja slike brez izgube podatkov. Da bi to dosegli, ta postopek uporablja dvižni filter, odvisno od pretvorbe 3D diskretne arhitekture VLSI valov.

2). Oblikovanje multiplikatorja SFQ s 4-bitnimi in učinkovito z visoko hitrostno strojno opremo

Ta projekt se v glavnem uporablja za izvedbo spremenjenega kodirnika kabine (MBE) s 4-bitnim SFQ multiplikator . Ta multiplikator zagotavlja dobre zmogljivosti v primerjavi z običajnim dajalnikom kabine. Ta projekt se v glavnem uporablja pri aplikacijah kritične zamude.

3). Kriptografski procesor, ki se uporablja v pametnih karticah z učinkovitim območjem

Ta projekt se uporablja za izvajanje treh kriptografskih algoritmov, ki jih podpirajo tako zasebni kot javni ključi, ki se uporabljajo v pametna kartica aplikacije za zagotavljanje izjemno varnega preverjanja in podatkov uporabnikov komunikacijo .

4). Množitelj za visoke hitrosti ali nizko porabo energije z napačno metodo zatiranja moči

Ta predlagani sistem filtrira neuporabne lažne signale aritmetičnih enot, da se prepreči nepotreben prenos podatkov, ki ne vpliva na zadnje računske rezultate. Ta sistem uporablja metodo SPST za multiplikatorje za doseganje nizke moči in hitrega prenosa podatkov.

5). Stiskanje in dekompresija algoritma podatkov brez izgub

Ta projekt se v glavnem izvaja za dvostopenjsko arhitekturo strojne opreme, odvisno od funkcije algoritma PDLZW (Parallel Dictionary LZW), pa tudi algoritma prilagodljivega Huffmanovega tipa, ki se uporablja za aplikacije stiskanja podatkov brez izgub in dekompresije brez izgub.

6). Arhitektura turbo dekoderja z nizko kompleksnostjo za energetsko učinkovite omrežja WSN

Predlagani sistem se uporablja za zmanjšanje celotne porabe energije med prenosom podatkov WSN-jev z algoritmom razgradnje LUT-Log-BCJR na osnovne operacije ACS (Add Compare Select).

7). Arhitektura VLSI za učinkovito odstranjevanje impulznega šuma slike

Ta predlagani sistem je bil v glavnem uporabljen za vizualno izboljšanje kakovosti slike, da bi se izognili možnostim poškodb z impulznim šumom za izvajanje učinkovite arhitekture VLSI s pomočjo filtra, ki ohranja rob.

8). Arhitektura procesorja v pomnilniku, ki se uporablja za stiskanje multimedije

Ta predlagani sistem zagotavlja arhitekturo z nizko zapletenostjo za procesor v pomnilniku za podporo večpredstavnostnim aplikacijam, in sicer stiskanje slik, video z uporabo ogromnih enojnih navodil, več podatkovnih konceptov in besedil z navodili.

9). Tehnika časovne sinhronizacije s hitrostjo prenosa simbolov za brezžične sisteme OFDM z majhno močjo

Ta predlagani sistem se uporablja predvsem za izboljšanje delovanja brezžičnega OFDM (Ortogonal Frequency Division) Multipleksiranje ) z zmanjšanjem moči celotnega osnovnega pasu s pomočjo ure generator s fazno nastavljivim in dinamičnim krmilnikom časovnega vzorčenja.

10). Izvedba multiplikatorja nizke porabe in visoke hitrosti na akumulatorju s seštevalnikom SPST in verilogom

Ta projekt se uporablja za oblikovanje MAC z nizko močjo in visoko hitrostjo (multiplikator in akumulator) s sprejetjem metode lažnega zatiranja moči na MBE (spremenjeni dajalnik kabine). Z uporabo te zasnove se je mogoče izogniti izgubi moči celotnega stikala.

11). Oblikovanje in izvedba robotskega procesorja z omogočanjem preprečevanja trkov s tehnologijo RFID

Predlagani sistem se v glavnem uporablja za izvajanje robotskega procesorja z zaščito pred trkom, da se prepreči fizično trčenje robotov v okolju več robotov. Ta algoritem se večinoma izvaja z uporabo tehnologije VHDL in RFID.

12). Načrtovanje logičnega vezja z učinkovitim napajanjem z uporabo adiabatske metode

Ta sistem učinkovito prikaže zasnovo logičnega vezja z adiabatsko metodo v primerjavi s konvencionalno zasnovo CMOS s pomočjo vezij, ki uporabljajo Vrata NAND & NOR . Z uporabo adiabatske metode lahko zmanjšamo odvajanje moči v omrežju in recikliramo shranjeno energijo v obremenitvenem kondenzatorju.

3). Šifrirni sistem za povečanje računalniške hitrosti sistema

Glavna namena tega projekta je izboljšati varnost prenosa podatkov za izboljšanje hitrosti računalništva z izvajanjem algoritma AES z uporabo FPGA. Tako lahko to simulacijo kot tudi matematično zasnovo izvedemo s pomočjo kode VHDL.

14). IP blok AHM ali naprednega visokozmogljivega vodila

Ta projekt se v glavnem uporablja za oblikovanje arhitekture Advanced Mikrokrmilnik Bus (AMB) z uporabo AHBN (Advanced High-Performance Bus). Ta projekt je mogoče zasnovati s kodo VHDL z izvajanjem blokov, kot sta master & save.

15). Večmodalni RF-oddajnik z večkanalnim DSM-jem

Ta sistem se v glavnem uporablja za zasnovo arhitekture večmodnega oddajnika in sprejemnika ter RF večkanalnega modulatorja Delta-Sigma. Ta predlagani sistem uporablja jezik VHDL za izvajanje dveh arhitektur.

16). Koncentrator stikala za izločanje z uporabo asinhronega načina prenosa

Z uporabo tega projekta lahko s pomočjo orodij, kot sta VHS in VHDL, oblikujemo stikalo za izločanje, ki temelji na asinhronem prenosu. To izklopno stikalo se lahko uporablja v omrežjih navideznega paketnega vezja, pa tudi v aplikacijah datagrama.

17). Vedenjska sinteza asinhronih vezij

Ta projekt se v glavnem uporablja za zagotavljanje tehnike vedenjske sinteze, ki se uporablja za asinhrona vezja. Obe predlogi, kot sta balsa in asinhrona izvedba, sta glavna elementa v zasnovi.

18). AMBA Design z uporabo združljivega krmilnika pomnilnika AHB

Ta projekt se uporablja za oblikovanje MC (pomnilniškega krmilnika), odvisno od AMBA (Advanced Microcontroller Bus Architecture) za nadzor sistemskega pomnilnika z uporabo glavnega pomnilnika, kot sta SRAM in ROM.

19). Carry Tree Adder Implementation

Nosilec dreves, ki temelji na zasnovi VLSI, se imenuje najboljši seštevalnik v primerjavi z običajnimi binarnimi seštevalniki. Seštevalniki, ki jih izvaja ta projekt, so raztegnjeno drevo, kogge-kamen in redek kogge-kamen.

20). Vrtenje s fiksnim kotom na osnovi zasnove CORDIC

Glavni koncept tega predlaganega sistema je obračanje vektorjev z uporabo fiksnih kotov. Ti koti so potrebni za igre, robotiko, obdelava slik itd. Z uporabo tega projekta lahko dosežemo vektorsko rotacijo z uporabo določenih kotov po zasnovi CORDIC (digitalni računalnik s koordinatnim vrtenjem).

21). Zasnova FIR filtra z porazdeljeno aritmetiko iskalne tabele

Ta predlagani sistem v glavnem izboljšuje FIR filter uspešnost z načrtovanjem z uporabo porazdeljene aritmetike tridimenzionalne iskalne tabele namesto množitelja. Tako je to zasnovo mogoče uporabiti s programsko opremo, kot sta FPGA in Xilinx.

22). Push-Pull impulzni zapahi z visoko hitrostjo in nizko močjo

Ta projekt se uporablja za izvedbo energetsko učinkovitih in visokozmogljivih impulznih zapahov, ki se v glavnem uporabljajo za sisteme VLSI z uporabo nove topologije. Ker je ta topologija v glavnem odvisna od končne faze push-pull, ki jo poganjata dva razdeljena pasova skozi pogojni impulzni generator.

23). Arithmetic Coder VLSI Arhitektura v SPIHT

Ta predlagani sistem izboljšuje pretok metode aritmetičnega kodiranja pri stiskanju slike v hierarhičnih drevesih (SPIHT) z visokohitrostno arhitekturo, odvisno od FPGA.

24). Dušenje hrupa EKG signala na osnovi FPGA

Ta projekt se uporablja za zadrževanje šuma znotraj EKG signalov skozi dva srednja filtra z 91 oziroma 7 vzorčnimi točkami. Ta postopek je torej mogoče doseči z izvajanjem Zasnova FPGA na podlagi kode VHDL.

25). Visoko zmogljiv procesor za skaliranje slik na osnovi VLSI z nizkimi stroški

Ta projekt se uporablja za izvajanje algoritma za procesor za spreminjanje velikosti slik na osnovi VLSI z manj pomnilnika in visoko zmogljivostjo. Predlagana zasnova sistema v glavnem vsebuje kombinacijo filtra, rekonfigurabilnih dinamičnih metod in skupne rabe strojne opreme za zmanjšanje stroškov.

26). Učinkovito načrtovanje in izvedba arhitekture Systolic Array

Glavni koncept tega projekta je oblikovanje modela strojne opreme, ki se uporablja za multiplikator sistoličnega polja. To polje lahko v glavnem uporabimo za izvajanje binarnega množenja s pomočjo platforme VHDL. Predlagano zasnovo sistema je mogoče izvesti z uporabo programske opreme FPGA in Isim.

27). QPSK Design & Synthesis z uporabo VHDL kode

QPSK je ena glavnih modulacijskih metod. Ta metoda se uporablja v aplikacijah satelitskega radia. To modulacijsko tehniko je mogoče izvesti z reverzibilnimi logičnimi vrati. Oblikovanje tehnike QPSK lahko izvedemo s pomočjo kode VHDL.

28). Zasnova in izvedba krmilnika DDR SDRAM z visoko hitrostjo

Predlagani sistem se uporablja za zasnovo krmilnika DDR SDRAM za prenos porušenih podatkov, odvisno od visoke hitrosti, za sinhronizacijo teh podatkov med vezjem vgrajenega sistema in DDR SDRAM. Z uporabo jezika VHDL lahko razvijemo kodo.

29). 32-bitno načrtovanje in izvedba procesorja RISC

Glavni koncept tega projekta je izvajanje 32-bitne različice RISC (računalnik z zmanjšanimi navodili) s pomočjo orodja, kot je XILINK VIRTEX4. V tem projektu je zasnovanih 16 nizov ukazov, kjer je mogoče vsako ukaz izvesti v enem ciklu CLK s petfazno metodo cevovoda.

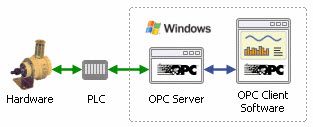

30). Izvedba avtobusnega mostu med AHB in OCP

Predlagani sistem se uporablja za načrtovanje vodila med dvema protokoloma, in sicer skupnim in standardnim. Zelo priljubljeni so komunikacijski protokoli, kot sta AHB (Advanced High-performance Bus) in OCP (Open Core Protocol), ki se uporabljajo v aplikacijah SoC (sistem na čipu) .

Ideje za projekte VLSI za študente tehnike

Seznam projektov VLSI, ki temeljijo na FPGA, MatLab, IEEE in Mini Projects za študente inženirjev, je naveden spodaj.

Projekti VLSI za študente M. Tech

Seznam projektov VLSI, ki temeljijo na M. Tech Student, vključuje naslednje.

- Območno učinkovita in zelo zanesljiva zasnova I0T pomnilniške celice na osnovi RHBD, ki se uporablja v vesoljskih aplikacijah

- Fazni detektor z večstopenjsko polovično hitrostjo, ki se uporablja za vezja CLK in obnovitev podatkov

- Primerjalnik z nizko porabo in visoko hitrostjo, ki se uporablja za natančne aplikacije

- Pretvornik napetosti z visoko zmogljivostjo in integriranim multipleksorjem

- Ternarni seštevalnik na osnovi CNTFET z visoko zmogljivostjo

- Oblika primerjalnika velikosti z majhno močjo

- Načrt praga logične lopute s trenutnim načinom za analizo zakasnitve

- Dekoderji z mešano logično linijo so zasnovani z nizko porabo in visoko zmogljivostjo

- Sleep Convention Logic Testability Design

- Preklopnik nivoja napetosti za aplikacije z dvojnim napajanjem z visoko hitrostjo in učinkovito porabo energije

- Načrtovanje in analiza dvosmernega primerjalnika nizke in nizke napetosti

- Dizajn flip-flop, ki temelji na impulzno sproženem z nizko porabo z uporabo metode prenosa signala

- Učinkovito načrtovanje vezij na podlagi FET-jev, ki jih je mogoče konfigurirati med izvajanjem

- Oblika primerjalnika velikosti z majhno močjo

- Analiza zakasnitve zasnov logičnih vrat s pragom trenutnega načina

The Projekti VLSI, ki temeljijo na FPGA za študente tehnike in CMOS VLSI oblikujejo mini projekte so navedeni spodaj.

- Oblikovanje in karakterizacija utrjenih vezij SEU za FPGA na osnovi SRAM

- Kompaktni CMIR-ov hibridni LOS-ov zasnova in potencialna aplikacija CMOS, ki se uporablja v FPGA

- Izvedba FPGA za merjenje razdalje na osnovi ultrazvočnega senzorja

- Izvedba FPGA za množitelj kabine s Spartan6 FPGA

- Diskretna valovita transformacija na osnovi dviganja s Spartan3 FPGA

- ARM krmilnik v robotiki z uporabo FPGA

- UART z večkanalnim FPGA

- Zatiranje šuma EKG signala z uporabo FPGA

- Implementacija FPGA na osnovi UTMI in plast protokola USB 2.0

- Izvajanje medianskega filtra s FPGA Spartan3

- Izvajanje FPGA na osnovi algoritma AES

- Sistem varnostnih opozoril na osnovi PIC za izvajanje FPGA s Spartan 3an

- Implementacija FPGA za načrtovanje krmilnika za sisteme daljinskega zaznavanja

- Komplet za obdelavo slik FPGA z uporabo filtriranja slik linearno in morfološko

- Implementacija medicinske fuzije slike Spartan3 FPGA

Seznam Mini projekti VLSI z uporabo kode VHDL vključuje naslednje.

- Primerjalnik z visoko hitrostjo z uporabo VLSI

- Množitelj s plavajočo vejico z uporabo VLSI

- Pretvorba binarnega v sivo na osnovi VLSI

- Digitalni filter

- CLK Gating na osnovi VLSI

- Vedski multiplikator

- CMOS FF z uporabo VLSI

- Arhitektura vzporednega procesorja, ki uporablja VLSI

- Full Adder na osnovi VLSI

- Zasnova pomnilnika DRAM / dinamičnega naključnega dostopa na osnovi VLSI

- Postavitev SRAM na osnovi VLSI

- Digitalni procesor signalov na osnovi VLSI

- Multiplexer na osnovi VLSI

- Oblikovanje enote MAC na osnovi VLSI

- Diferenciator na osnovi VLSI

- FFT na osnovi VLSI ali hitra Fourierjeva transformacija

- Arhitektura diskretne kosinusne transformacije, ki temelji na VLSI

- 16-bitni multiplikator z uporabo VLSI19

- Oblikovanje vmesnika FIFO na osnovi VLSI

- Hitri pospeševalnik na osnovi VLSI

VLSI projekti, ki uporabljajo MATLAB in Xilinx

Seznam projektov VLSI, ki temeljijo na projektih MATLAB in VLSI z uporabo Xilinxa, vključuje naslednje.

- Oblikovanje in analiza CDMA modema z MATLAB-om

- Zasnova FIR filtra z uporabo VHDL v analizi FPGA in MATLAB

- ModelSim & Matlab ali Simulink na osnovi simulacije sistema za avtomobilsko tehniko

- Seštevalniki na osnovi Xilinxa, kot je Ripple Carry & Carry Skip

- Aritmetična enota na osnovi 32-bitne plavajoče vejice

- ALU s plavajočo vejico

- Procesor RISC, ki temelji na 32-bitni različici

- Konvolucijske zmožnosti pravokotne kode

- Prodajni avtomat na osnovi Xilinxa in Veriloga

- Vzporedni predponski seštevalniki na osnovi Xilinxa z 256-bitnimi različicami

- Protokol za medsebojno overjanje z Xilinxom

- Struktura dostopa z enim ciklom za logični test z uporabo Xilinxa

- UTMI in protokol USB2.0 na osnovi Xilinx

- Konfiguracija stiskanja in dekompresije podatkov z uporabo Xilinx FPGA

- FPGA na osnovi BIST in Spartan Series, ki temeljijo na Xilinxu

- IIR filter na osnovi MATLAB & VLSI

- FIR filter z uporabo MATLAB

Projekti IEEE

The seznam IEEE VLSI projektov je navedeno spodaj.

- Brezžični sistem za domačo avtomatizacijo, ki temelji na VLSI, z uporabo Bluetootha

- Odstranjevanje impulznega šuma znotraj slike z uporabo učinkovite arhitekture VLSI

- Arhitektura procesorja v pomnilniku za multimedijsko stiskanje

- Nadzor temperaturnega sistema z uporabo oblaka in interneta stvari

- Implementacija sistema OFDM z IFFT in FFT

- Oblikovanje in izvedba Hammingove kode z Verilogom

- Prepoznavanje prstnih odtisov na osnovi VHDL z uporabo Gaborjevega filtra

- Aritmetične funkcije Preslikava z ROM-om, odvisno od približevalnih pristopov

- Analiza učinkovitosti in učinkovitosti nizke gostote dekodirnika za preverjanje paritete v aplikacijah z majhno porabo

- Arhitekture FFT s povratnim napovedom cevnega Radix-2k

- Natikače za aplikacije VLSI z uporabo tehnologije CMOS z visoko zmogljivostjo

- Zasnova FIR filtra z iskalno tabelo po porazdeljeni aritmetiki

- Nizkocenovni in izboljšani procesor za skaliranje slik na osnovi VLSI

- ASIC Implementacija in oblikovanje turbinskega kodirnika in dekoderja Advance s 3GPP LTE

- Push-Pull impulzni zapahi z pogonsko nizko močjo in visoko hitrostjo

- Izboljšano skeniranje pri preskušanju nizke porabe energije

- Arithmetic Coder VLSI Arhitektura za SPIHT

- Izvajanje VHDL za UART

- VLSI regulator napetosti z nizkim izpadom

- Flash ADC dizajn z izboljšano primerjalno shemo

- Nizkoenergijski multiplikacijski dizajn s slogom sestavljene konstantne zakasnitve

- Dvostranski primerjalnik z visoko zmogljivostjo in nizko močjo

- Flash Storage sistem z visoko zmogljivostjo, odvisno od vmesnega pomnilnika in navideznega pomnilnika

- FF z nizko porabo, ki temelji na pristopu Sleepy Stack

- LFSR optimizacija moči za BIST z nizko porabo energije, implementirana v HDL

- Oblikovanje in izvedba prodajnih avtomatov s Verilog HDL

- Zasnova akumulatorja, ki temelji na ustvarjanju vzorca s tremi utežmi z LP-LSFR

- Reed-Solomon dekoder z visoko hitrostjo in nizko kompleksnostjo

- Hitrejša tehnika oblikovanja multiplikatorjev Dadda

- Digitalni sprejemnik FM radia na osnovi demodulacije

- Ustvarjanje testnega vzorca s shemami BIST

- Izvajanje arhitekture VLSI z visokohitrostnim cevovodom

- Zasnova protokola OCP na vgrajenem vodilu z uporabo vodila

- Fazni frekvenčni detektor in zasnova črpalke za polnjenje, ki se uporablja za visokofrekvenčno fazno zaklenjeno zanko

- Predpomnilnik in zasnova krmilnika predpomnilnika z VHDL

- Izvedba nizkoenergijskih kompresorjev 3-2 in 4-2 na osnovi ASTRAN

- Predplačniški sistem za obračun električne energije z uporabo vgrajenega dizajna

- Izvajanje prekrivanja z uporabo logične celice in njene analize moči

- Carry Look Ahead Adder z različno analizo zmogljivosti bitov z uporabo VHDL

- Oblika sloja podatkovne povezave z Wi-Fi MAC Protokoli

- Izvajanje FPGA za protokol vzajemne overitve z modularno aritmetiko

- Generacija signala PWM z uporabo FPGA in spremenljivim delovnim ciklom

Projekti v realnem času

Seznam VLSI projekti v realnem času v glavnem vključujejo mini projekte VLSI z uporabo kode VHDL in programe programske opreme VLSI za študente inženirjev ECE.

- Pragmatična integracija vrstnega predpomnilnika SRAM v heterogeni 3-D arhitekturi DRAM z uporabo TSV

- Vgrajena tehnika samotestiranja za diagnosticiranje napak z zakasnitvijo v grozdnih poljskih programabilnih nizih vrat

- ASIC Oblikovanje kompleksnega multiplikatorja

- Nizkocenovna izvedba VLSI za učinkovito odstranjevanje impulznega hrupa

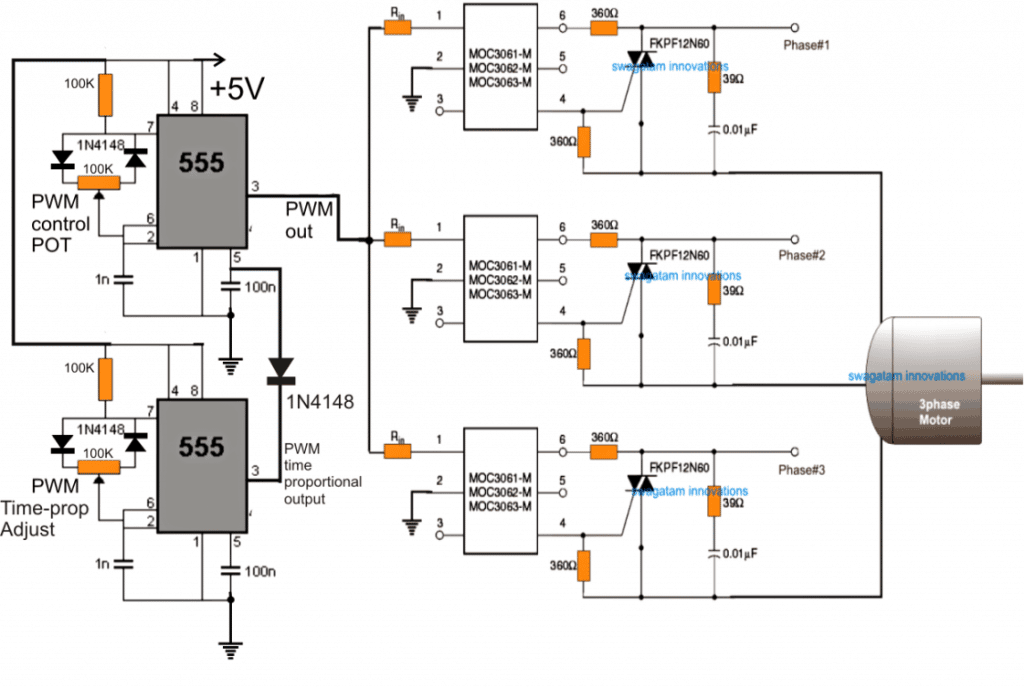

- Na osnovi FPGA Vesoljski vektor PWM Krmilna IC za trifazni asinhronski pogon

- Vpeljava VLSI samodejnega korelatorja in algoritma CORDIC za omrežje WLAN na osnovi OFDM

- Samodejno odstranjevanje ceste z uporabo satelitskih posnetkov visoke ločljivosti

- Oblika VHDL za segmentacijo slik z uporabo Gaborjevega filtra za odkrivanje bolezni

- Turbo dekodirna arhitektura nizke zapletenosti za energetsko učinkovita brezžična senzorska omrežja

- Izboljšanje zmožnosti konvolucije pravokotne kode z uporabo implementacije FPGA

- Načrtovanje in izvedba plavajoče vejice ALU

- CORDIC zasnova za fiksni kot vrtenja

- Kode izdelka Reed-Solomon za implementacijo krmilnika NAND Flash na čipu FPGA

- Statistično izboljšanje izkoristka bralnega dostopa SRAM z uporabo vezij negativne kapacitivnosti

- Upravljanje porabe omrežnih vmesnikov MIMO v mobilnih sistemih

- Zasnova standarda za šifriranje podatkov za šifriranje podatkov

- Nizka poraba energije in površinsko učinkovit prenosnik

- Sinteza in implementacija UART z uporabo kod VHDL

- Izboljšane arhitekture za enoto seštevanja odštevanja s plavajočo vejico

- 1-bitni popolnoma digitalni oddajnik na osnovi FPGA, ki uporablja modulacijo Delta-Sigma z RF izhodom za SDR

- Optimizacija uporabe verižnega iskanja v dekoderju BCH za prenos z visoko stopnjo napak

- Digitalno oblikovanje oddajnika DS-CDMA z uporabo veriga HDL in FPGA

- Načrtovanje in izvedba učinkovite arhitekture sistoličnih nizov

- Algoritem učenja dinamike robotov na osnovi VLSI

- Vsestranska zasnova multimedijske funkcionalne enote s tehniko lažnega dušenja moči

- Zasnova avtobusnega mostu med AHB in OCP

- Vedenjska sinteza asinhronih vezij

- Optimizacija hitrosti spremenjenega Viterbijevega dekoderja na osnovi FPGA

- Izvajanje vmesnika I2C

- Hitro / nizkoenergijski množitelj z napredno tehniko lažnega dušenja moči

- Vpenjanje navidezne napajalne napetosti napajalnih vezij za aktivno zmanjšanje uhajanja in zanesljivost oksida v vratih

- Napajalno učinkovit usmerjevalnik na osnovi FPGA za programsko določen radio

- Arhitektura VLSI in FPGA prototipiranje digitalnega fotoaparata za zaščito in preverjanje pristnosti slike

- Operacija Izboljšanje notranjega robota

- Načrtovanje in izvedba omrežja za permutacijo ON-Chip za večprocesorski sistem-On-Chip

- Metoda sinhronizacije časovne hitrosti za nizkoenergijske brezžične sisteme OFDM

- Krmilnik DMA (neposreden dostop do pomnilnika) z uporabo VHDL / VLSI

- Prekonfigurabilni FFT z uporabo arhitekture na osnovi CORDIC za sprejemnike MIMI-OFDM

- Lažna tehnika zatiranja napajanja za multimedijske / DSP aplikacije

- Učinkovitost kod BCH pri vodnih žigovih digitalnih slik

- Krmilnik SD-RAM z dvojno hitrostjo prenosa podatkov

- Uporaba Gaborjevega filtra za prepoznavanje prstnih odtisov z uporabo veriga HDL

- Oblikovanje praktičnega nanometrskega odvečnega merila prek ozaveščene standardne knjižnice celic za izboljšano odvečno z 1 stopnjo vstavljanja

- Algoritem za stiskanje in dekompresijo podatkov brez izgub in njegova strojna arhitektura

- Okvir za odpravljanje večbitnih mehkih napak

- Učinkovito stiskanje testnih podatkov na osnovi Viterbija

- Izvajanje blokov FFT / IFFT za OFDM

- Stiskanje slike na osnovi valov s postopnim kodiranjem VLSI

- Vpeljava VLSI popolnoma pipeliranega multiplikatorja manj 2d DCT / IDCT arhitektura za Jpeg

- Emulacija napak na osnovi FPGA sinhronih sekvenčnih vezij

Tu gre torej za seznam projektov VLSI za inženiring, študentje M.Tech-a, ki so v pomoč pri izbiri teme zadnjega letnika projekta. Po porabi dragocenega časa med pregledovanjem tega seznama verjamemo, da imate dokaj dobro idejo, da izberete temo projekta, ki ste jo izbrali s seznama projektov VLSI, in upamo, da imate dovolj samozavesti, da se lotite katere koli teme seznam. Za nadaljnje podrobnosti in pomoč pri teh projektih nam lahko pišete v spodnjem oddelku za komentarje. Tukaj je vprašanje za vas, kaj je VHDL?

Foto kredit

- VLSI projekti avtorja set-tech