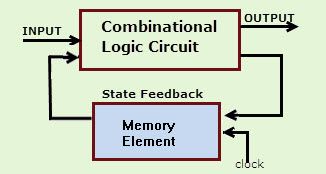

V kombinacijskih vezjih se različni logični vhodi uporabljajo za načrtovanje dajalnika, multiplekserja, dekoderja in de-multiplekserja. Ta vezja imajo nekatere značilnosti, kot je izhod tega vezja odvisen predvsem od ravni, ki so kadar koli na vhodnih terminalih. To vezje ne vsebuje nobenega pomnilnika. Prejšnje stanje vhoda nima vpliva na trenutno stanje tega vezja. Vhodi in izhodi kombinacijskega vezja so „n“ št. vhodov & 'm' št. izhodov. Nekatera kombinacijska vezja so polovični seštevalnik in polni seštevalec, odštevalnik, dajalnik, dekoder, multiplekser in demultiplekser. Ta članek obravnava pregled polovičnega seštevalnika in celotnega seštevalnika ter njegovo delo s tabelami resnic.

Kaj je Adder?

Seštevalec je digitalno logično vezje v elektroniki, ki se pogosto uporablja za dodajanje številk. V mnogih računalnikih in drugih vrstah procesorjev se seštevalniki uporabljajo celo za izračun naslovov in z njimi povezanih dejavnosti ter za izračun indeksov tabel v ALU in celo za uporabo v drugih delih procesorjev. Te je mogoče zgraditi za številne numerične predstavitve, na primer presežek-3 ali binarno kodirano decimalno mesto. Seštevalniki so v osnovi razvrščeni v dve vrsti: pol seštevalnik in polni seštevalec.

Kaj je vezje pol adderja in polnega seštevalnika?

Vezje polovičnega seštevalnika ima dva vhoda: A in B, ki dodata dve vhodni števki in ustvarita prenos in vsoto. Polno seštevalno vezje ima tri vhode: A in C, ki dodata tri vhodne številke in ustvari prenos in vsoto. Ta članek vsebuje podrobne informacije o tem, kaj je namen pol seštevalnika in polni seštevalnik v tabelarnih oblikah in celo v vezjih. Že omenjeno je, da je glavni in ključni namen seštevalcev dodajanje. Spodaj je podrobno teorija pol seštevalnika in polnega seštevalnika.

Osnovni pol seštevalnik in polni seštevalec

Half Adder

Torej, ko pridemo do scenarija polovičnega seštevalnika, doda dve binarni števki, kjer se vhodni bit imenujeta povečanje in seštevanje, rezultat pa bo dva izhoda, en je vsota, drugi pa prenos. Za izvedbo operacije seštevanja se XOR uporabi na obeh vhodih, AND gate pa na obeh vhodih za ustvarjanje prenosa.

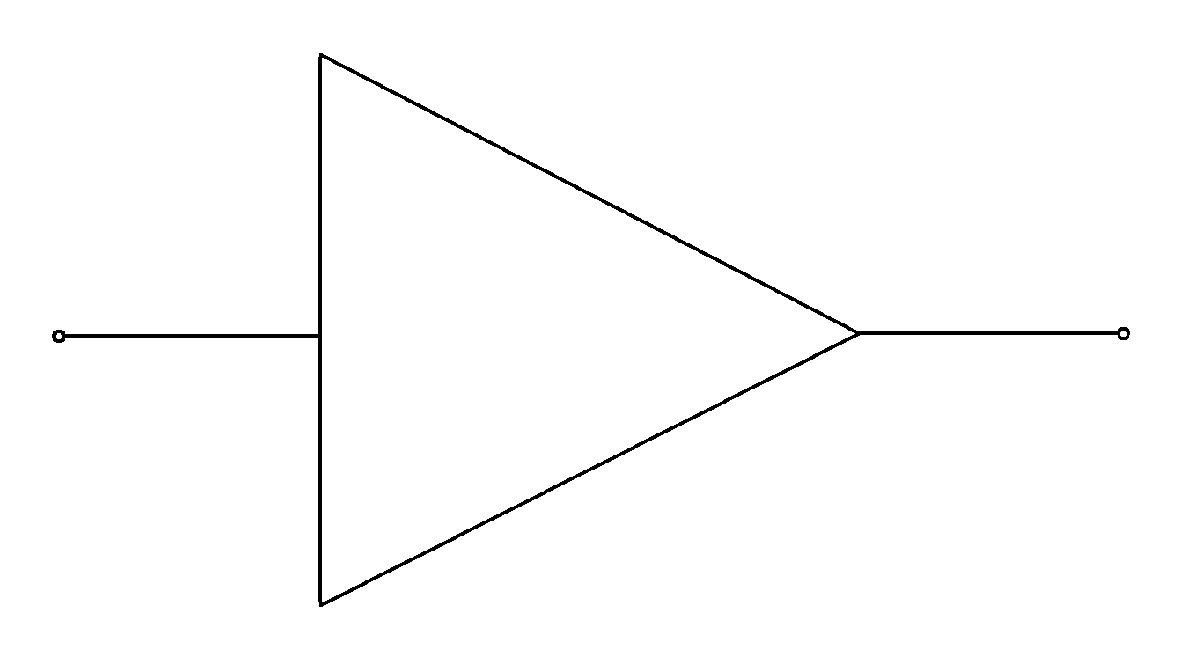

HA Funkcijski diagram

Medtem ko v celotnem vezju seštevalnika doda 3 enobitna števila, pri čemer lahko dva od treh bitov označimo kot operanda, drugega pa kot vnesenega bita. Proizvedena izhodna moč je 2-bitna in se lahko nanje sklicuje do kot izhodni prenos in vsota.

Z uporabo polovičnega seštevalnika lahko s pomočjo logičnih vrat oblikujete preprost dodatek.

Oglejmo si primer dodajanja dveh posameznih bitov.

2-bitni tabela resnic na pol seštevalnika je spodaj:

Tabela resnic za polovico seštevkov

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

To so najmanj možne enobitne kombinacije. Toda rezultat za 1 + 1 je 10, rezultat vsote je treba znova zapisati kot 2-bitni izhod. Tako lahko enačbe zapišemo kot

0 + 0 = 00

0 + 1 = 01

1 + 0 = 01

1 + 1 = 10

Izhod '1' od '10' je izvedba. „SUM“ je običajna moč, „CARRY“ pa izvedba.

Zdaj je jasno, da je mogoče 1-bitni seštevalnik enostavno implementirati s pomočjo vrat XOR za izhod 'SUM' in Vrata AND za 'Carry'.

Na primer, ko moramo dodati dva 8-bitna bajta skupaj, ga lahko izvedemo z uporabo logičnega vezja s polnim seštevalnikom. Polseštevalnik je uporaben, če želite dodati eno binarno količino.

Način za razvijanje dvomestnih seštevalnikov bi bil izdelava tabele resnic in njeno zmanjšanje. Ko želite narediti trimestno dvomestno seštevalnik, se operacija dodajanja polovičnega seštevalnika izvede dvakrat. Na podoben način, ko se odločite za izdelavo štirimestnega seštevalnika, se postopek izvede še enkrat. S to teorijo je bilo jasno, da je izvedba preprosta, vendar je razvoj dolgotrajen proces.

Najenostavnejši izraz uporablja izključno funkcijo OR:

Vsota = A XOR B

Carry = A IN B

HA logični diagram

In enakovreden izraz v smislu osnovnih AND, OR in NOT je:

SUM = A.B + A.B ’

Koda VHDL za pol seštevalca

Entiteta je

Vrata (a: v STD_LOGIC

b: v STD_LOGIC

sha: ven STD_LOGIC

cha: ven STD_LOGIC)

konec ha

Arhitektura Obnašanje zgornjega vezja je

začeti

sha<= a xor b

št<= a and b

konec Vedenjsko

Številka IC s polovičnim števcem

Izvedbo polovičnega seštevalnika je mogoče izvesti z visokohitrostnimi digitalnimi logičnimi integriranimi vezji CMOS, kot je serija 74HCxx, ki vključuje SN74HC08 (7408) in SN74HC86 (7486).

Omejitve polovičnega števca

Glavni razlog za klic teh binarnih seštevalnikov, kot je Half Adders, je v tem, da ni nobenega obsega, ki bi vključeval prenosni bit z uporabo prejšnjega bita. To je torej glavna omejitev HA, ki so se nekoč uporabljale kot binarni seštevalnik, zlasti v situacijah v realnem času, ki vključujejo dodajanje več bitov. To omejitev je torej mogoče premagati z uporabo celotnih seštevalnikov.

Polni seštevalec

Ta seštevalnik je težko uporabiti v primerjavi s polovičnim seštevalnikom.

Funkcijski diagram celotnega seštevalnika

Razlika med polovičnim seštevalnikom in polnim seštevalnikom je v tem, da ima polni seštevalnik tri vhode in dva izhoda, medtem ko ima polovični seštevalec le dva vhoda in dva izhoda. Prva dva vhoda sta A in B, tretji vhod pa je vhod kot C-IN. Ko je zasnovana logika s polnim seštevalnikom, jih nanižete osem, da ustvarite seštevalnik v celotnem bajtu in kaskadno prenese bit iz enega seštevalnika v drugega.

Tabela resnic FA

Izhodni prenos je označen kot C-OUT, običajni izhod pa S kot SUM.

Z zgornjim tabela resnic s polnim seštevalnikom , izvedbo celotnega vezja seštevalnika lahko razumemo enostavno. SUM 'S' se izdela v dveh korakih:

- S XORingom zagotovljenih vhodov 'A' in 'B'

- Rezultat A XOR B je nato XORed s C-IN

To ustvari SUM in C-OUT je resničen le, če sta dva od treh vhodov HIGH, potem bo C-OUT HIGH. Torej lahko izvedemo polno seštevalno vezje s pomočjo dveh polovičnih seštevalnih vezij. Sprva se bo polovični seštevalec uporabljal za dodajanje A in B za ustvarjanje delne vsote, logika seštevalnika v drugi polovici pa se bo uporabljala za dodajanje C-IN vsoti, ki jo proizvede prva polovica seštevalnika, da se dobi končni izhod S

Če katera od logik polovičnega seštevalnika povzroči prenos, bo izhodni prenos. Torej bo C-OUT funkcija ALI izhodov polovičnega seštevalnika Carry. Oglejte si izvajanje celotnega vezja seštevalnika, prikazano spodaj.

Logični diagram celotnega seštevalnika

Izvedba večjih logičnih diagramov je možna z zgornjo logiko celotnega seštevalnika, za predstavitev operacije se večinoma uporablja preprostejši simbol. Spodaj je prikazana enostavnejša shematska predstavitev enobitnega polnega seštevalnika.

S to vrsto simbola lahko skupaj seštejemo dva bita, pri čemer vzamemo prenos iz naslednjega nižjega reda velikosti in pošljemo prenos v naslednji višji red velikosti. V računalniku mora biti za večbitno operacijo vsak bit predstavljen s popolnim seštevalnikom in ga je treba dodati hkrati. Če želite torej dodati dve 8-bitni številki, boste potrebovali 8 popolnih seštevalnikov, ki jih lahko oblikujete s kaskadnimi dvema od 4-bitnih blokov.

Half Adder in Full Adder z uporabo K-Map

Celo izhodne vrednosti vsote in prenosa za polovični seštevalec lahko dobimo tudi z metodo Karnaughovega zemljevida (K-map). The polovični seštevalec in polni seštevalnik, logični izraz je mogoče dobiti preko K-map. K-karta za te seštevalnike je obravnavana spodaj.

K-karta polovičnega seštevalnika je

HA K-zemljevid

Celoten seštevalnik K-Map je

FA K-Map

Logični izraz SUM in Carry

Logični izraz vsote (S) lahko določimo na podlagi vhodnih podatkov, omenjenih v tabeli.

= A’B’Cin + A ’B CCin’ + A B’Cin ’+ AB Cin

= Cin (A’B ’+ AB) + Cin’ (A’B + A B ’)

= Cin EX-OR (A EX-ALI B)

= (1,2,4,7)

Logični izraz prenosa (Cout) je mogoče določiti na podlagi vhodov, omenjenih v tabeli.

= A’B Cin + AB’Cin + AB Cin ’+ ABCin

= AB + BCin + ACin

= (3, 5, 6, 7)

Z zgoraj omenjenimi tabelami resnic je mogoče dobiti rezultate, postopek pa je:

Kombinacijsko vezje združuje različne vhode v vezju, kjer so ti lahko dajalnik, dekoder, multiplekser in demultiplekser . Značilnosti kombinacijskih vezij so naslednje.

- Izhod v katerem koli trenutku temelji le na nivojih, ki so prisotni na vhodnih terminalih.

- Ne uporablja nobenega pomnilnika. Prejšnje stanje vnosa ne vpliva na trenutno stanje vezja.

- Lahko ima poljubno število vhodov in m število izhodov.

Kodiranje VHDL

Kodiranje VHDL za polni seštevalnik vključujejo naslednje.

entiteta full_add je

Vrata (a: v STD_LOGIC

b: v STD_LOGIC

cin: v STD_LOGIC

vsota: ven STD_LOGIC

cout: out STD_LOGIC)

konec full_add

Arhitektura Vedenje full_add je

komponenta ha je

Vrata (a: v STD_LOGIC

b: v STD_LOGIC

sha: ven STD_LOGIC

cha: ven STD_LOGIC)

končna komponenta

signal s_s, c1, c2: STD_LOGIC

začeti

HA1: karta zemljevida ha (a, b, s_s, c1)

HA2: zemljevid pristanišča ha (s_s, cin, sum, c2)

stroškov<=c1 or c2

konec Vedenjsko

The razlika med pol seštevalnikom in polnim seštevalnikom je, da polovica seštevalnika daje rezultate, polni seštevalec pa polovico seštevalnika, da ustvari kakšen drug rezultat. Podobno, medtem ko je Full-Adder dva polovična seštevalnika, je Full-Adder dejanski blok, ki ga uporabljamo za ustvarjanje aritmetičnih vezij.

Nosite dodajalce Lookahead

V konceptu valovnih sesalnih sklopov so bitji, ki so potrebni za dodajanje, takoj na voljo. Medtem ko mora vsak odsek seštevalnika zadržati čas za prihod prenosa iz prejšnjega bloka seštevalnika. Zaradi tega traja več časa za izdelavo SUM in CARRY, saj vsak odsek v vezju čaka na prihod vhoda.

Na primer, da dostavi izhod za n-ti blok, mora prejeti vhod iz (n-1) -tega bloka. In ta zakasnitev se ustrezno imenuje zakasnitev širjenja.

Da bi premagali zakasnitev seštevalnika valov, nosilec je bil uveden. Tu lahko z uporabo zapletene strojne opreme zmanjšamo zakasnitev širjenja. Spodnji diagram prikazuje seštevalnik prenosa, ki uporablja celotne seštevalnike.

Nosite Lookahead s polnim seštevalnikom

Tabela resnic in ustrezne izhodne enacbe so

| TO | B | C | C + 1 | Stanje |

| 0 | 0 | 0 | 0 | No Carry Ustvari |

| 0 | 0 | 1. | 0 | |

| 0 | 1. | 0 | 0 | |

| 0 | 1. | 1. | 1. | No Carry Razširite |

| 1. | 0 | 0 | 0 | |

| 1. | 0 | 1. | 1. | |

| 1. | 1. | 0 | 1. | Nositi Ustvari |

| 1. | 1. | 1. | 1. |

Enačba širjenja prenosa je Pi = Ai XOR Bi, generiranje prenosa pa Gi = Ai * Bi. S temi enačbami lahko enačbe vsote in prenosa predstavimo kot

SUM = Pi XOR Ci

Ci + 1 = Gi + Pi * Ci

Gi dostavi prenos samo, če sta vhoda Ai in Bi enaka 1, ne da bi upošteval vhodni prenos. Pi je povezan s širjenjem prenosa iz Ci v Ci + 1.

Razlika med pol seštevalca in polnega seštevalca

The razlika med polovičnim seštevalnikom in tabelo s polnim seštevalnikom je prikazano spodaj.

| Half Adder | Polni seštevalec |

| Half Adder (HA) je kombinacijsko logično vezje in to vezje se uporablja za dodajanje dveh enobitnih številk. | Full Adder (FA) je kombinacijsko vezje in to vezje se uporablja za dodajanje treh enobitnih številk. |

| V HA, ko je prenos izveden iz prejšnjega seštevanja, ni mogoče dodati naslednjega koraka. | V FA, ko je prenos ustvarjen iz prejšnjega seštevanja, ga je mogoče dodati v naslednji korak. |

| Polovični seštevalnik vključuje dva logična vhoda, kot sta vrata AND in EX-OR. | Popolni seštevalnik vključuje dva vrata EX-OR, dva vrata OR ali dva vrata IN. |

| Vhodna bita v polovičnem seštevalniku sta dva kot A, B. | Vhodni bit v celotnem seštevalniku so trije, kot so A, B & C-in |

| Polovična seštevalna in enačba seštevalnika je S = a⊕b C = a * b | Popoln logični izraz seštevalnika je S = a ⊕ b⊕Cin Cout = (a * b) + (Cin * (a⊕b)). |

| HA se uporablja v računalnikih, kalkulatorjih, napravah za digitalno merjenje itd. | FA se uporablja v digitalnih procesorjih, večbitnem seštevanju itd. |

The ključne razlike med polovičnim seštevalnikom in polnim seštevalnikom so obravnavane v nadaljevanju.

- Polovični seštevalec ustvari vsoto in prenos z dodajanjem dveh binarnih vhodov, celotni seštevalec pa se uporablja za ustvarjanje vsote in prenosa z dodajanjem treh binarnih vhodov. Arhitektura strojne opreme na pol seštevalnika in polnega seštevalnika ni enaka.

- Glavna značilnost, ki razlikuje HA in FA, je ta, da v HA ni takega dogovora, da bi zadnji dodatek obravnavali kot njegov vnos. Vendar FA najde določen vhodni stolpec, kot je Cin, da razmisli o nosilnem bitu zadnjega dodanega.

- Dva seštevalnika bosta pokazala razliko glede na komponente, uporabljene v vezju za njegovo konstrukcijo. Polovični seštevalniki (HA) so zasnovani s kombinacijo dveh logičnih vrat, kot sta AND & EX-OR, medtem ko je FA zasnovan s kombinacijo treh AND, dveh XOR in enega OR vrat.

- V bistvu HA delujejo na dva-dva vhoda 1-bitov, medtem ko FA delujejo na treh vhodih 1-bitov. Polovični seštevalec se uporablja v različnih elektronskih napravah za ocenjevanje seštevanja, medtem ko se polni seštevalnik uporablja v digitalnih procesorjih za dodajanje dolgega bita.

- Podobnosti med tema dvema seštevalnikoma sta, da sta HA in FA kombinacijska digitalna vezja, zato ne uporabljajo nobenega pomnilniškega elementa, kot so zaporedna vezja. Ta vezja so za aritmetično delovanje nujna za dodajanje binarnega števila.

Izvedba celotnega seštevalnika z uporabo polovičnih seštevalcev

Izvedbo FA lahko izvedemo prek dveh polovičnih seštevalnikov, ki sta logično povezana. Blokovni diagram tega je lahko prikazan spodaj, ki prikazuje povezavo FA s pomočjo dveh polovičnih seštevalnikov.

Enačbe vsote in prenosa iz prejšnjih izračunov so

S = A ‘B’ Cin + A ’BC’ v + ABCin

Cout = AB + ACin + BCin

Enačbo vsote lahko zapišemo kot.

Cin (A’B ‘+ AB) + C‘ in (A‘B + A B ’)

Torej, vsota = Cin EX-OR (A EX-OR B)

Cin (A EX-ALI B) + C’in (A EX-ALI B)

= Cin EX-OR (A EX-ALI B)

Cout lahko zapišemo takole.

COUT = AB + ACin + BCin.

Cout = AB + + razočaranja BCin (A + A)

= ABCin + AB + ACin + A ’B Cin

= AB (1 + Cin) + ACin + A ’B Cin

= A B + ACin + A ’B Cin

= AB + ACin (B + B ’) + A’ B Cin

= ABCin + AB + A’B Cin + A ’B Cin

= AB (Cin + 1) + A B Cin + A ’B Cin

= AB + AB ’Cin + A’ B Cin

= AB + Cin (AB ’+ A’B)

Zato je COUT = AB + Cin (A EX-ALI B)

Glede na zgornji dve enačbi vsote in prenosa lahko FA vezje izvedemo s pomočjo dveh HA in OR vrat. Shema vezja polnega seštevalnika z dvema polovicama seštevalnikov je prikazana zgoraj.

Celoten seštevalnik z uporabo dveh polovičnih seštevalnikov

Popoln dizajn seštevalnika z uporabo NAND Gates

Vrata NAND so ena vrsta univerzalnih vrat, ki se uporabljajo za izvedbo kakršne koli logične zasnove. FA vezje z diagramom vrat NAND je prikazano spodaj.

FA z uporabo vrat NAND

FA je enostaven enobitni seštevalec in če želimo izvesti dodajanje n-bitnega, potem n ne. enobitnih FA-jev je treba uporabiti v obliki kaskadne povezave.

Prednosti

The prednosti pol seštevalnika in polnega seštevalnika vključujejo naslednje.

- Najpomembnejši namen polovičnega seštevalnika je dodati dve enobitni številki

- Polni seštevalniki imajo možnost dodajanja nosilnega bita, ki je rezultat prejšnjega dodajanja

- S polnim seštevalnikom je mogoče implementirati ključna vezja, kot so seštevalnik, multiplekser in številna druga

- Polna seštevalna vezja porabijo minimalno moč

- Prednosti polnega seštevalnika pred polovičnim seštevalnikom so, da se s polnim seštevalnikom premaga pomanjkljivost polovičnega seštevalnika, ker se polovični seštevalec uporablja predvsem za dodajanje dveh 1-bitnih številk. Polovični seštevalniki ne dodajo nosilnega kosa, zato je za premagovanje tega polnega seštevalnika uporabljen. V Full adder lahko dodamo tri bite in ustvari dva izhoda.

- Oblikovanje seštevalnikov je preprosto in je osnovni gradnik, tako da je eno-bitni dodatek lahko razumljiv.

- Ta seštevalnik lahko pretvorite v polovico odštevalnika z dodajanjem pretvornika.

- Z uporabo celotnega seštevalnika lahko dosežemo visoko moč.

- Visoka hitrost

- Zelo močan za skaliranje napetosti

Slabosti

The pomanjkljivosti pol seštevalnika in polnega seštevalnika vključujejo naslednje.

- Poleg tega polovičnega seštevalnika pred prenosom ni mogoče uporabiti, zato ni uporaben za kaskadno dodajanje večbitnega.

- Da bi odpravili to pomanjkljivost, je treba FA dodati tri 1 bit.

- Ko je FA uporabljen v obliki verige, kot je RA (Ripple Adder), lahko pogonsko zmogljivost izhoda zmanjšamo.

Aplikacije

Aplikacije pol seštevalnika in polnega seštevalnika vključujejo naslednje.

- Dodajanje binarnih bitov lahko izvede polovični seštevalnik z uporabo ALU v računalniku, ker uporablja seštevalnik.

- Kombinacijo polovičnega seštevalnika lahko uporabimo za načrtovanje celotnega vezja seštevalnika.

- V kalkulatorjih se uporabljajo polovični seštevalniki in za merjenje naslovov in tabel

- Ta vezja se uporabljajo za obdelavo različnih aplikacij znotraj digitalnih vezij. V prihodnosti ima ključno vlogo pri digitalni elektroniki.

- FA vezje se uporablja kot element v mnogih velikih vezjih, kot je Ripple Carry Adder. Ta seštevalnik hkrati doda število bitov.

- FA se uporabljajo v enoti za aritmetično logiko (ALU)

- FA se uporabljajo v aplikacijah, povezanih z grafiko, kot je GPU (Graphics Processing Unit)

- Ti se uporabljajo v vezju množenja za izvedbo množenja izvedb.

- V računalniku se za generiranje naslova pomnilnika in za izdelavo programskega kontrapunkta za nadaljnja navodila uporablja Arithmetic Logic Unit z uporabo polnih seštevalnikov.

Tako se vsakič, ko se doda dve binarni številki, najprej dodajo števke najmanj bitov. Ta postopek je mogoče izvesti s polovičnim seštevalnikom, ker je najpreprostejši n / w, ki omogoča dodajanje dveh 1-bitnih številk. Vhodi tega seštevalnika so binarne številke, izhodi pa so vsota (S) in prenašanje (C).

Kadar je vključeno število števk, se omrežje HA uporabi samo za povezovanje najmanj števk, saj HA ne more dodati nosilne številke iz prejšnjega razreda. Polni seštevalnik je mogoče definirati kot osnovo vseh digitalnih aritmetičnih naprav. To se uporablja za dodajanje treh 1-mestnih številk. Ta seštevalnik vključuje tri vhode, kot so A, B in Cin, medtem ko sta izhoda Sum in Cout.

Sorodni koncepti

The koncepti, povezani s polovičnim seštevalnikom in polnim seštevalnikom samo ne držite se enega samega namena. Veliko jih uporabljajo v številnih aplikacijah, nekaj sorodnih pa je omenjenih:

- Številka IC s polovičnim seštevalnikom in polnim seštevalnikom

- Razvoj 8-bitnega seštevalnika

- Kakšni so previdnostni ukrepi za polovično seštevanje?

- JAVA Aplet Ripple Carry Adderja

Zato gre tukaj za teorija pol seštevalnika in polnega seštevalnika skupaj s tabelami resnic in logičnimi diagrami je prikazana tudi zasnova celotnega seštevalnika z uporabo polovičnega vezja. Mnogi od pol seštevalnik in polni seštevalnik pdf Na voljo so dokumenti za napredne informacije o teh konceptih. Poleg tega je pomembno vedeti kako je izveden 4-bitni polni seštevalnik ?