Glavna pomanjkljivost kombinacijsko vezje je, ne uporablja nobenega pomnilnika za shranjevanje sedanjega in prejšnjega stanja. Prejšnje stanje vhoda torej nima nobenega vpliva na trenutno stanje vezja. Medtem ko ima zaporedno vezje pomnilnik, se lahko izhod razlikuje glede na vhod. Ta vrsta vezij uporablja predhodni vhod, izhod, uro in pomnilniški element. Tu so lahko pomnilniški elementi zapah ali natikači. Zaporedna vezja so zasnovana na različne načine, na primer z uporabo ROM-jev in zrcal, PLA-jev, CPLD (kompleksna programabilna logična naprava) , FPGA (Field Programmable Gate Array) . V tem članku bomo razpravljali samo o tem, kako oblikovati zaporedno vezje z uporabo PLA.

Blokovni diagram zaporednega vezja, kot je prikazano spodaj:

Blok diagram zaporednega vezja

Oblikovanje zaporednega vezja z uporabo PLA

Zaporedna vezja je mogoče uresničiti z uporabo PLA (programabilnih logičnih nizov) in natikačev. Pri tej zasnovi je lahko dodelitev države pomembna, ker lahko uporaba dobre državne dodelitve zmanjša zahtevano število izrazov izdelka in s tem zmanjša zahtevano velikost PLA. Izraz izdelka, opredeljen kot zveza dobesednih besedil, kjer je vsaka dobesedna spremenljivka ali njena negacija.

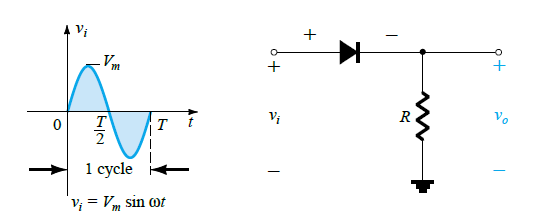

Razmislimo o zasnovi pretvornika kod. Tabelo stanja, prikazano spodaj v tabeli, je mogoče uresničiti z uporabo enega in treh PLA natikači kot je prikazano pod sliko. Ta konfiguracija vezja je zelo podobna zasnovi na flip-flopu na osnovi ROM-a, le da je ROM nadomeščen s PLA ustrezne velikosti. Dodelitev države vodi do spodnje tabele resnic. To tabelo bi lahko shranili v PLA s štirimi vhodi, 13 izrazi izdelkov in štirimi izhodi, vendar bi to v primerjavi s 16-besednim ROM-om ponudilo malo manjše velikosti.

| X Q1 Q2 Q3 | Z D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

Tabela: Tabela resnice

PRISUTNO DRŽAVA

| NASLEDNJA DRŽAVA X = 0,1 | PRISUTNO IZHOD (Z) |

| TO | B C | 1 0 |

B C | D E In E | 1 0 0 1 |

D JE | H H H M | 0 1 1 0 |

H M | A A TO - | 0 1 1 - |

Tabela: Državna tabela

Oblikovanje zaporednih vezij z uporabo PLA

Vhodne izhodne enačbe, ki jih je izpeljal Karnaugh Map

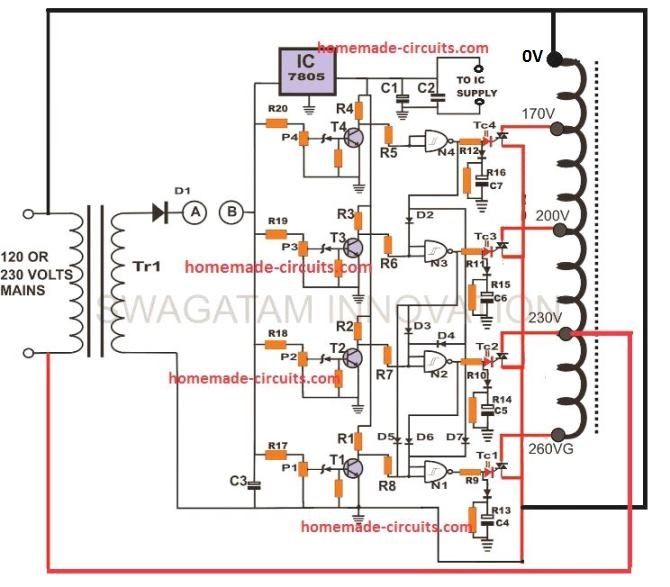

Ker je sedem stanj, so potrebne tri natikače D. Tako je potrebno vezje PLA s 4 vhodi in 4 izhodi. Če upoštevamo dodelitev stanja pretvornika kode, lahko nastalo izhodno enačbo in D vhodne enačbe flip-flop, ki izhajajo iz Karnaugh-a, zapišemo v naslednje enačbe

D1 = Q1 + = Q2 '

D2 = Q2 + = Q2 '

D3 = Q3 + = Q1 Q2 Q3 = X ”Q1 Q3” = X Q1 ”Q2”

Z = X ”Q3” + X Q3

| X Q1 Q2 Q3 | Z D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 enajst

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

Tabela PLA, ki ustreza tem enačbam, je podana v zgornji tabeli. To tabelo je mogoče uresničiti z uporabo PLA s štirimi vhodi, sedmimi izrazi izdelka in štirimi izhodi. Za prvo preverjanje delovanja zgornje zasnove predpostavimo, da sta X = 0 in Q1Q2Q3 = 000. S tem izberete vrstice - - 0- in 0 - - -0 v tabeli, tako da je Z = 0 in D1D2D3 = 100. Po aktivnem robu ure je Q1Q2Q3 = 100. Če je naslednji vhod X = 1, so izbrane vrstice - - 0 - in - 1- -, tako da je Z = 0 in D1D2D3 = 110. Po aktivnem robu ure je Q1Q2Q3 = 110.

Programabilna logična matrika (PLA)

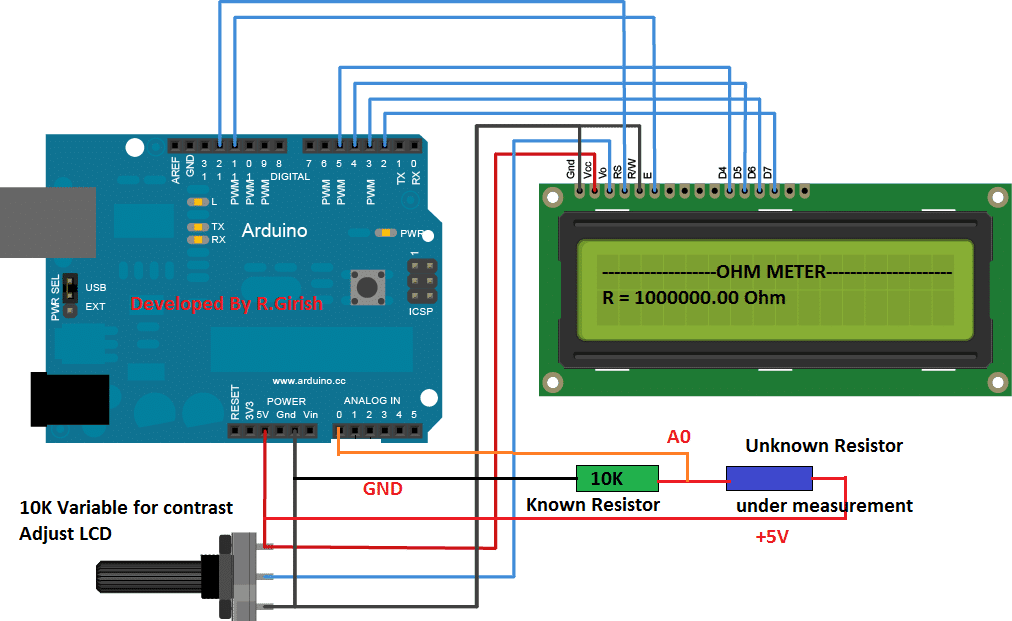

Programmable Logic Array je programabilna logična naprava. Običajno se uporablja za izvajanje kombinacijskih logičnih vezij. PLA ima nabor programabilnih ravnin AND (AND matrika), ki se povezujejo z nizom programabilnih AL ploskev (OR matrika), ki jih lahko nato začasno dopolnimo, da dobimo izhod. Ta postavitev omogoča sintezo velikega števila logičnih funkcij v vsota izdelkov (SOP) kanonične oblike. Preprost blokovni diagram PLA je podan spodaj.

Blok diagram PLA

Glavna razlika med PLA in PAL (programabilna matrična logika) je,

PLA: Oboje IN ravnina in ALI ravnina so programabilni.

PAL: Programirana je lahko le ravnina AND, medtem ko je ravnina OR fiksna.

Za boljše razumevanje PLA tukaj obravnavamo spodnji primer.

Poskusimo implementirati ti funkciji f1 in f2 sta podani kot

Vhodi x1, x2, x3 in njihovi ustrezni dopolnjeni signali so podani na programabilno ravnino AND, tam bomo dobili izhode ravnine AND kot P1, P2, P3, imenovane minterme. Nato se ti signali dajo na programabilno ALI ravnino, da se ustvari zahtevana izhodna funkcija f1 in f2 (vsota izdelkov). Spodnja slika opisuje izvedbo PLA na ravni vrat za dano funkcionalnost.

Izvajanje PLA

To je vse o načrtovanju zaporednih vezij z uporabo PLA. Menimo, da so informacije v tem članku koristne za boljše razumevanje tega koncepta. Poleg tega kakršna koli vprašanja v zvezi s tem člankom ali kakršna koli pomoč v izvajanje električnih in elektronskih projektov , se lahko obrnete na nas s komentarjem v spodnjem oddelku za komentarje. Tukaj je vprašanje za vas, Kaj pomeni zaporedno vezje?